## INTERBUS Conformance Test

# **Basic Test**

### **Manufacturer Declarations**

| Manufacturer Declaration for Devices With RS-485 Copper Interface and<br>Basic Test | 3  |

|-------------------------------------------------------------------------------------|----|

| Manufacturer Declaration for Devices With INTERBUS Loop Interface                   | 9  |

| Manufacturer Declaration for Devices With Optical Fiber Interface                   | 15 |

The "test steps" for the test object are described in the second column and the number of the relevant checklist is given in the first column. The person carrying out the test only has to enter the test result in the "OK" column. Any comments are entered in the "OK\*)" field. The assigned text appears at the bottom of the table as a footnote.

| No. Test Step | OK *) |

|---------------|-------|

|---------------|-------|

The following applies to the assessment of the test steps:

Y Yes: Criterion met.

All specifications for this test step must be met.

Y- Yes-: Criterion met - deviation permitted.

For deviations that influence neither the electrical nor the time response of the interface, the person carrying out the test may positively assess this part of the test.

Example: Pull-down resistor of 2.7 kOhm instead of 3.3 kOhm is used.

- No: Criterion not met, deviation not permitted. According to the person carrying out the test, the deviations influence the electrical or time response of the interface in such a way that the test step must be assessed negatively.

- Inconclusive: Criterion not to be taken into consideration.

The criterion does not apply to the test object and this test step is not relevant to the overall assessment.

For the overall assessment criterion to be "Passed", each test step must receive either the "Criterion met" or "Criterion met - deviation permitted" assessment. If deviations are detected, they must be noted and the final decision must be justified.

#### Manufacturer Declaration for Devices With RS-485 Copper Interface and Basic Test

#### Test report number:

| No.          | Test Step                                                                                                                                                                                                                                            | OK *) |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <b>HE</b> 1. | <ul> <li>RS-485 driver/receiver</li> <li>Has an approved type or alternative *) been used with the specified circuit for the RS-485 driver/receiver in the INTERBUS data path?</li> <li>Which? (please enter here)</li> </ul>                        |       |

| <b>HE</b> 2. | All resistors have a tolerance of +/-1%.                                                                                                                                                                                                             |       |

| HE 3.        | <ul> <li>Optocoupler</li> <li>Has an approved type or alternative *) been used with the specified circuit for the optocoupler in the INTERBUS data path?</li> <li>Which? (please enter here)</li> </ul>                                              |       |

| <b>HE</b> 4. | <ul> <li>Does the series resistor in the LED circuit correspond to the value specified for the optocoupler?</li> </ul>                                                                                                                               |       |

| <b>HE</b> 5. | - Does the pull-up resistor at the output of the optocoupler correspond to the value specified for the optocoupler?                                                                                                                                  |       |

| <b>HE</b> 6. | <ul> <li>Is each optocoupler equipped with a 100 nF blocking<br/>capacitor?</li> </ul>                                                                                                                                                               |       |

| HE 7.        | <ul> <li>Connector pin assignment</li> <li>Has an approved type of connector with defined pinning<br/>(labeling, assignment, order of the connections especially<br/>for the terminals) been used? *)</li> <li>Which? (please enter here)</li> </ul> |       |

| <b>HE</b> 8. | <ul> <li>Additional wiring for INTERBUS data lines</li> <li>Have any other active or passive components (e.g.,<br/>Transsorb or suppressor diodes, filters, etc.) been used on/in</li> </ul>                                                         |       |

|              | the INTERBUS data path in addition to those listed?                                                                                                                                                                                                  |       |

3/20

| <b>HE</b> 9.  | 24 V supply voltage loop from input to output                                                                                                                                                                                              |       |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|               | <ul> <li>All 3 signals FE, +24 V, and 0 V must be looped through<br/>without any additional elements (fuses, resistors, etc.) from<br/>the input to the output.</li> </ul>                                                                 |       |

| <b>HE</b> 10. | <ul> <li>The 24 V supply voltage connection must be designed according to the defined continuous current.</li> <li>Installation remote bus I<sub>Nom</sub>= 4.5 A</li> </ul>                                                               |       |

| <b>HE</b> 12. | <ul> <li>The 24 V supply voltage connection must be designed according to the defined continuous current.</li> <li>Rugged Line I<sub>Nom</sub>= 16 A</li> </ul>                                                                            |       |

| HE 13.        | <ul> <li>Data connection from the Rugged Line connector</li> <li>The length of the shielded cable from the Rugged Line connector to the device electronics should not exceed 20 cm (7.87 in.).</li> </ul>                                  |       |

| <b>HE</b> 14. | HE 1.                                                                                                                                                                                                                                      |       |

| <b>HE</b> 15. | - The isolation voltage between the individual electrically isolated areas is at least 350 V AC.                                                                                                                                           |       |

| <b>HE</b> 16. | <ul> <li>*) If FE of the outgoing interface is not directly connected<br/>with GND, a capacitor/resistor combination (R &lt;= 1 MOhm, C<br/>approximately 15nF) (parallel circuit) can be selected as an<br/>alternative. HE 2.</li> </ul> |       |

| HE 17.        | <ul> <li>Has an approved type of protocol chip or an approved<br/>alternative been used? *)</li> </ul>                                                                                                                                     |       |

| HE 18.        | <ul> <li>If the chip has optical control, is it disabled?<br/>(RF1=RF2=1 for SUPI3 OPC)</li> </ul>                                                                                                                                         |       |

| <b>HE</b> 19. | <ul> <li>Are all the unused inputs for the protocol chip (including MFPs) connected with a defined voltage?</li> </ul>                                                                                                                     |       |

| <b>HE</b> 20. | - <b>3Chex</b> - For remote bus devices (for devices with special requirements, only is approved by the INTERBUS Club.)                                                                                                                    |       |

| HE 21.        | - During bus startup, the Generation 4 master reads in the<br>"Microprocessor Not Ready" ID code and generates the<br>"Incorrect initialization of the protocol chip by the<br>microprocessor" error message 0C73 and 0D700D73             |       |

| 4/20          |                                                                                                                                                                                                                                            | 05.01 |

| HE 22.        | - The expected ID code can be read in after bus startup.                                                                                                                                                                                |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HE 23.        | <ul> <li>The power-up reset input of the slave protocol chip and the<br/>assigned expansion blocks are wired with a 1 kOhm, 100 nF<br/>filter.</li> </ul>                                                                               |  |

| <b>HE</b> 24. | <ul> <li>The voltage monitoring circuit ensures that the reset input for<br/>the protocol chip and the assigned expansion blocks has a<br/>low signal with a voltage of U Nom minus the tolerance (5 V -<br/>10%, typical).</li> </ul>  |  |

| HE 25.        | <ul> <li>The reset time realized by the voltage monitoring circuit is at<br/>least 2 oscillator clock cycles (125 ns at 16 MHz, typical) for<br/>the balanced oscillator and at specified voltage.</li> </ul>                           |  |

| <b>HE</b> 26. | <ul> <li>For direct and indirect wiring of the reset input, ensure that the components used in the entire voltage area of the voltage monitor are operating properly.</li> <li>Standard logic gates are <u>not</u> suitable.</li> </ul> |  |

| HE 27.        | <ul> <li>The power-up reset of the slave protocol chip and the<br/>assigned expansion blocks is never influenced by the<br/>software, an LCA or microprocessor.</li> </ul>                                                              |  |

| <b>HE</b> 28. | <ul> <li>The resistance between +5 V and the reset pin of the IBS<br/>SUPI 3 OPC protocol chip family is <b>never</b> lower than 600<br/>Ohm.</li> </ul>                                                                                |  |

| <b>HE</b> 29. | <ul> <li>When using the reset pin of the IBS SUPI 3 OPC protocol<br/>chip family as an input:<br/>The resistance between GND and the reset pin of the protocol<br/>chip does not exceed 600 Ohm on a "0" signal.</li> </ul>             |  |

| <b>HE</b> 30. | <ul> <li>When using the reset pin of the IBS SUPI 3 OPC protocol<br/>chip family as an output:<br/>The resistance between GND and the reset pin of the protocol<br/>chip is not less than 23 kOhm.</li> </ul>                           |  |

| HE 31.        | <ul> <li>A clock (e.g., quartz oscillator) applied at the protocol chip<br/>meets the requirements given in the INTERBUS protocol chip<br/>data sheet. **)</li> </ul>                                                                   |  |

| HE 32.        | <ul> <li>A quartz used meets the requirements given in the<br/>INTERBUS protocol chip data sheet. ***)</li> </ul>                                                                                                                       |  |

| <b>HE</b> 33. | <ul> <li>A quartz oscillating circuit does not supply other components<br/>with its clock.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>HE</b> 34. | - The clockline is not influenced by other logic or software.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| <b>HE</b> 35. | - The clockline circuit is tested for the entire permissible temperature range of the device +/- 10%.                                                                                                                                                                                                                                                                                                                                             |  |

| <b>HE</b> 36. | <ul> <li>Additional capacitors for the IBS SUP13 quartz<br/>OPC quartz inputs are not available.</li> </ul>                                                                                                                                                                                                                                                                                                                                       |  |

| HE 37.        | <ul> <li>Have approved types or an approved alternative been used<br/>for the expansion blocks? *)</li> </ul>                                                                                                                                                                                                                                                                                                                                     |  |

| <b>HE</b> 38. | - One data output for the register expansion does not drive more than 4 inputs.                                                                                                                                                                                                                                                                                                                                                                   |  |

| <b>HE</b> 39. | - If a buffer is used for the register expansion signal ClkExR, have identical buffers been used for signal ToExR2?                                                                                                                                                                                                                                                                                                                               |  |

| <b>HE</b> 40. | <ul> <li>Are the register expansion registers in close proximity to the protocol chip on the same board?</li> <li>The tracks are &lt; 5 cm (1.97 in.).</li> </ul>                                                                                                                                                                                                                                                                                 |  |

| HE 41.        | - Are the Latch, Data (IN&OUT), Clock, and /ResReg signals<br>for the register expansion blocks only used by the INTERBUS<br>slave protocol chip or by the reset logic that controls it?                                                                                                                                                                                                                                                          |  |

| HE 42.        | <ul> <li>Diagnostic signals</li> <li>The required diagnostic LEDs for this device type (see table) are directly connected to the slave protocol chip and are not controlled via software (with the exception of TR). *)</li> </ul>                                                                                                                                                                                                                |  |

| <b>HE</b> 43. | <ul> <li>The green U<sub>L</sub> LED is directly controlled by the voltage monitor.</li> </ul>                                                                                                                                                                                                                                                                                                                                                    |  |

| HE 44.        | <ul> <li>If the protocol chip diagnostic input I/O Error ("/StatErr" for<br/>IBS SUPI 3) is used, the events that are generated by these<br/>diagnostic messages are simulated and the response is<br/>checked at the INTERBUS master. ****)<br/>The data pattern 0xF0 is output for all OUT data bytes of the<br/>test object. This means it is also possible to test module error<br/>messages by short-circuiting a digital output.</li> </ul> |  |

| <b>HE</b> 45. | - If the protocol chip diagnostic input <i>Reconfiguration Request</i><br>("Conf" for IBS SUPI 3) is used, the events that are generated<br>by this diagnostic message are simulated and the response<br>is checked at the INTERBUS master. ****)            |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>HE</b> 46. | - If the protocol chip diagnostic input <i>MAU Warning</i> ("MAUWS,<br>MAUWR, MAUWH" for IBS SUPI 3) is used, the events that<br>are generated by this diagnostic message are simulated and<br>the response is checked at the INTERBUS master. ****)         |  |

| <b>HE</b> 47. | - If the protocol chip diagnostic input <i>Microprocessor</i><br><i>Watchdog</i> ("/StatErr" for IBS SUPI 3) is used, the events that<br>are generated by this diagnostic message are simulated and<br>the response is checked at the INTERBUS master. ****) |  |

| <b>HE</b> 48. | - If the protocol chip diagnostic output <i>Alarm</i> ("Alarm" for IBS SUPI 3) is used, the events that are generated by this diagnostic signal at the device are checked. ****)                                                                             |  |

| <b>HE</b> 49. | - If the protocol chip diagnostic output <i>Module Acknowledge</i> ("/ModAck" for IBS SUPI 3) is used, the events that are generated by this diagnostic signal at the device are checked. ****)                                                              |  |

| <b>HE</b> 50. | <ul> <li>Additional PCP error codes</li> <li>Additional PCP error codes defined by the manufacturer are always assigned error class "8", error code "0" in the additional code.</li> </ul>                                                                   |  |

Test object (only for PCP devices)

Manufacturer

Name

Signature

### Manufacturer Declaration for Devices With INTERBUS Loop Interface

### Test report number:

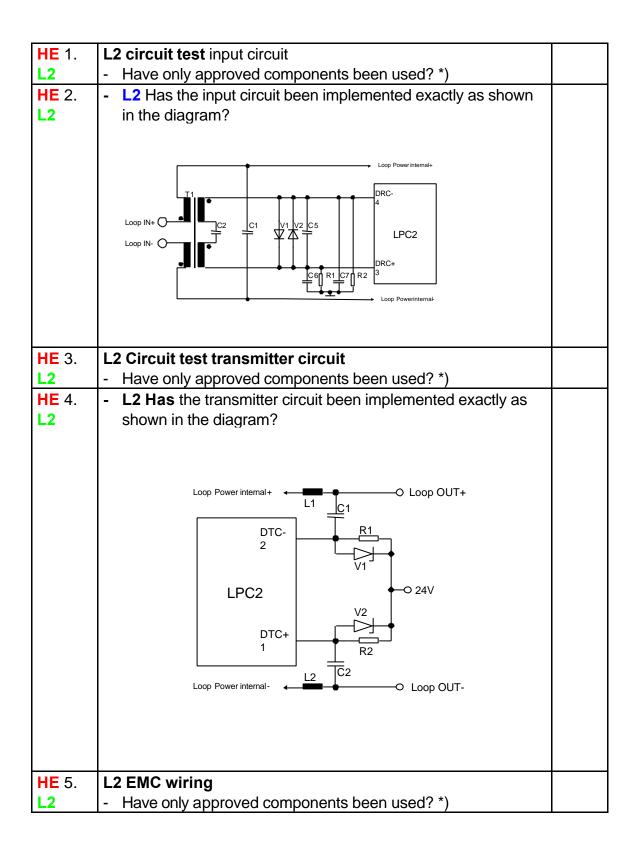

| No.          | Test Step                                                                                                                                                                                                                                                                                                                                                                                                                                         | OK *) |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| HE 1.        | <ul> <li>The isolation voltage between the individual electrically<br/>isolated areas is at least 350 V AC.</li> </ul>                                                                                                                                                                                                                                                                                                                            |       |

| HE 2.        | <ul> <li>Are all the unused inputs for the protocol chip (including<br/>MFPs) connected with a defined voltage?</li> </ul>                                                                                                                                                                                                                                                                                                                        |       |

| <b>HE</b> 3. | - 3Chex - For remote bus devices (for devices with special requirements, only is approved by the INTERBUS Club.)                                                                                                                                                                                                                                                                                                                                  |       |

| <b>HE</b> 4. | - During bus startup, the Generation 4 master reads in the<br>"Microprocessor Not Ready" ID code and generates the<br>"Incorrect initialization of the protocol chip by the<br>microprocessor" error message 0C73 and 0D700D73                                                                                                                                                                                                                    |       |

| <b>HE</b> 5. | - The expected ID code can be read in after bus startup.                                                                                                                                                                                                                                                                                                                                                                                          |       |

| <b>HE</b> 6. | <ul> <li>Diagnostic signals</li> <li>The required diagnostic LEDs for this device type (see table) are directly connected to the slave protocol chip and are not controlled via software (with the exception of TR).</li> </ul>                                                                                                                                                                                                                   |       |

| HE 7.        | <ul> <li>If the protocol chip diagnostic input I/O Error ("/StatErr" for<br/>IBS SUPI 3) is used, the events that are generated by these<br/>diagnostic messages are simulated and the response is<br/>checked at the INTERBUS master. ****)<br/>The data pattern 0xF0 is output for all OUT data bytes of the<br/>test object. This means it is also possible to test module error<br/>messages by short-circuiting a digital output.</li> </ul> |       |

10/20

| <b>HE</b> 6.  | - L2 Has the EMC circuit been implemented exactly as shown                                                                                   |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| L2            | in the diagram?                                                                                                                              |  |

|               | EMI Protection for Loop IN<br>Standard - EMI Protection (optional)                                                                           |  |

|               | Loop Power internal+ 9                                                                                                                       |  |

|               |                                                                                                                                              |  |

|               |                                                                                                                                              |  |

|               |                                                                                                                                              |  |

|               | Rt1                                                                                                                                          |  |

|               |                                                                                                                                              |  |

|               | $ \begin{array}{c c} \hline FE \end{array} \begin{array}{c c} \hline FE \end{array} \begin{array}{c c} \hline FV^2 \end{array} \end{array} $ |  |

|               |                                                                                                                                              |  |

|               |                                                                                                                                              |  |

|               | Loop Power internal-                                                                                                                         |  |

| <b>HE</b> 7.  | L2 Additional wiring for INTERBUS Loop data lines                                                                                            |  |

| L2            |                                                                                                                                              |  |

|               | - Have <b>any other</b> active and passive components (e.g.,                                                                                 |  |

|               | Transorb or suppressor diodes, filters, etc.) been                                                                                           |  |

|               | implemented on/in the INTERBUS data path in addition to<br>those currently used?                                                             |  |

| <b>HE</b> 8.  | L2 Maximum load                                                                                                                              |  |

| L2            | - The device takes the INTERBUS Loop voltage for no more than 1.8 A.                                                                         |  |

| <b>HE</b> 9.  | - L2 The maximum current taken from the INTERBUS Loop                                                                                        |  |

| L2            | supply is stated in the user documentation (user manual).                                                                                    |  |

|               |                                                                                                                                              |  |

| <b>HE</b> 10. | L2 Direct link                                                                                                                               |  |

| L2            | - In this specific area of application the Loop IN to Loop OUT                                                                               |  |

|               | direct link is less than 0.15 Ohm (RL1 + RL2 + 4*contact resistance + conductor paths).                                                      |  |

| <b>HE</b> 11. | <ul> <li>L2 In this specific area of application the Loop IN to Loop</li> </ul>                                                              |  |

| L2            | OUT connection is a continuous current of 5 A.                                                                                               |  |

| <b>HE</b> 12. | - L2 INTERBUS Loop signals are looped back from the input                                                                                    |  |

| L2            | to the output without additional (excluding approved) elements                                                                               |  |

|               | (fuses, resistors, etc.).                                                                                                                    |  |

| HE 13.        | - L2 INTERBUS Loop signals are looped back from the input                                                                                    |  |

| L2            | to the output without additional (excluding approved) elements (fuses, resistors, etc.).                                                     |  |

|               | (10000, 1001010, 610.).                                                                                                                      |  |

| -             |                                                                  |  |

|---------------|------------------------------------------------------------------|--|

| <b>HE</b> 14. | L2 Functional earth ground connection                            |  |

| L2            | - The module electronics only have one functional earth ground   |  |

|               | to prevent ground loops.                                         |  |

| <b>HE</b> 15. | L2 Potential levels                                              |  |

| L2            | - An additional voltage for the I/O supply is led to the device, |  |

|               | which is also electrically isolated from the Loop supply.        |  |

| <b>HE</b> 16. | L2 Protocol chip                                                 |  |

| L2            | - Has an approved type of protocol chip or an approved           |  |

|               | alternative been used? *)                                        |  |

| HE 17.        | HE 1.                                                            |  |

| L2            |                                                                  |  |

| <b>HE</b> 18. | - L2 Is a green LED connected directly to the DIAG pin?          |  |

| L2            |                                                                  |  |

| <b>HE</b> 19. | - L2 Is pin 5 of IBS LPC2 connected via at least one capacitor   |  |

| L2            | (3.3µF 10µF)?                                                    |  |

| <b>HE</b> 20. | - L2 Are Pin6, Pin7, and Pin8 switched with GND?                 |  |

| L2            |                                                                  |  |

| <b>HE</b> 21. | HE 2.                                                            |  |

| L2            |                                                                  |  |

| HE 22.        | - Has an approved quartz type or an approved alternative *)      |  |

| L2            | been used?                                                       |  |

| <b>HE</b> 23. | - The quartz pulse circuit does not supply other components      |  |

| L2            | with its clock.                                                  |  |

| <b>HE</b> 24. | HE 3.                                                            |  |

| L2            |                                                                  |  |

| <b>HE</b> 25. | - L2 The clockline circuit is tested with the same permissible   |  |

| L2            | temperature range +/- 10% of the device.                         |  |

| L             |                                                                  |  |

Manufacturer

### **INTERBUS Club** Conformance test and certification V2.0

Name

Signature

## Manufacturer Declaration for Devices With Optical Fiber Interface

### Test report number

| No.          | Test Step                                                                                                                                                                                                                                  | OK *) |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <b>HE</b> 1. | 24 V supply <b>voltage loop</b> from input to output                                                                                                                                                                                       |       |

|              | - All 3 signals FE, +24 V, and 0 V must be looped through without any additional elements (fuses, resistors, etc.) from the input to the output.                                                                                           |       |

| <b>HE</b> 2. | <ul> <li>The 24 V supply voltage connection must be designed according to the defined continuous current.</li> <li>Installation remote bus I<sub>Nom</sub>= 4.5 A</li> </ul>                                                               |       |

| <b>HE</b> 3. | <ul> <li>The 24 V supply voltage connection must be designed according to the defined continuous current.</li> <li>Rugged Line I<sub>Nom</sub>= 16 A</li> </ul>                                                                            |       |

| HE 4.        | <ul> <li>Data connection from the Rugged Line connector</li> <li>The length of the shielded cable from the Rugged Line connector to the device electronics should not exceed 20 cm (7.87 in.).</li> </ul>                                  |       |

| <b>HE</b> 5. | - Is the shield of the data connection cable for the Rugged Line connector connected to the GND on both sides?                                                                                                                             |       |

| <b>HE</b> 6. | <ul> <li>The isolation voltage between the individual electrically<br/>isolated areas is at least 350 V AC.</li> </ul>                                                                                                                     |       |

| HE 7.        | <ul> <li>*) If FE of the outgoing interface is not directly connected<br/>with GND, a capacitor/resistor combination (R &lt;= 1 MOhm, C<br/>approximately 15nF) (parallel circuit) can be selected as an<br/>alternative. HE 3.</li> </ul> |       |

| <b>HE</b> 8. | <ul> <li>Are all the unused inputs for the protocol chip (including<br/>MFPs) connected with a defined voltage?</li> </ul>                                                                                                                 |       |

| <b>HE</b> 9. | - 3Chex - For remote bus devices (for devices with special requirements, only is approved by the INTERBUS Club.)                                                                                                                           |       |

| <b>HE</b> 10. | - During bus startup, the Generation 4 master reads in the<br>"Microprocessor Not Ready" ID code and generates the<br>"Incorrect initialization of the protocol chip by the<br>microprocessor" error message 0C73 and 0D700D73                 |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>HE</b> 11. | - The expected ID code can be read in after bus startup.                                                                                                                                                                                       |

| HE 12.        | - The power-up reset input of the slave protocol chip and the assigned expansion blocks are wired with a 1 kOhm, 100 nF filter.                                                                                                                |

| <b>HE</b> 13. | <ul> <li>The voltage monitoring circuit ensures that the reset input for<br/>the protocol chip and the assigned expansion blocks has a<br/>low signal with a voltage of U Nom minus the tolerance (5 V -<br/>10%, typical).</li> </ul>         |

| <b>HE</b> 14. | - The reset time realized by the voltage monitoring circuit is at least 2 oscillator clock cycles (125 ns at 16 MHz, typical) for the balanced oscillator and at specified voltage.                                                            |

| <b>HE</b> 15. | <ul> <li>For direct and indirect wiring of the reset input, ensure that the components used in the entire voltage area of the voltage monitor are <u>operating</u> properly.</li> <li>Standard logic gates are <u>not</u> suitable.</li> </ul> |

| <b>HE</b> 16. | - The power-up reset of the slave protocol chip and the assigned expansion blocks is never influenced by the software, an LCA or microprocessor.                                                                                               |

| <b>HE</b> 17. | <ul> <li>The resistance between +5 V and the reset pin of the IBS<br/>SUPI 3 OPC protocol chip family is <b>never</b> lower than 600<br/>Ohm.</li> </ul>                                                                                       |

| <b>HE</b> 18. | <ul> <li>When using the reset pin of the IBS SUPI 3 OPC protocol<br/>chip family as an input:<br/>The resistance between GND and the reset pin of the protocol<br/>chip does not exceed 600 Ohm on a "0" signal.</li> </ul>                    |

| HE 19.        | <ul> <li>When using the reset pin of the IBS SUPI 3 OPC protocol<br/>chip family as an output:<br/>The resistance between GND and the reset pin of the protocol<br/>chip is not less than 23 kOhm.</li> </ul>                                  |

| HE 20.        | <ul> <li>A clock (e.g., quartz oscillator) applied at the protocol chip<br/>meets the requirements given in the INTERBUS protocol chip<br/>data sheet. **)</li> </ul>                                                                          |

| <b>HE</b> 21. | - A quartz used meets the requirements given in the INTERBUS protocol chip data sheet. ***)                                                                                                                                                    |

| HE 22.        | <ul> <li>A quartz oscillating circuit does not supply other components<br/>with its clock.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>HE</b> 23. | - The clockline is not influenced by other logic or software.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| <b>HE</b> 24. | - The clockline circuit is tested for the entire permissible temperature range of the device +/- 10%.                                                                                                                                                                                                                                                                                                                                             |  |

| HE 25.        | <ul> <li>Additional capacitors for the IBS SUP13 quartz<br/>OPC quartz inputs are not available.</li> </ul>                                                                                                                                                                                                                                                                                                                                       |  |

| HE 26.        | <ul> <li>Have approved types or an approved alternative been used<br/>for the expansion blocks? *)</li> </ul>                                                                                                                                                                                                                                                                                                                                     |  |

| <b>HE</b> 27. | <ul> <li>One data output for the register expansion does not drive<br/>more than 4 inputs.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |  |

| HE 28.        | <ul> <li>If a buffer is used for the register expansion signal ClkExR,<br/>have identical buffers been used for signal ToExR2?</li> </ul>                                                                                                                                                                                                                                                                                                         |  |

| HE 29.        | <ul> <li>Are the register expansion registers in close proximity to the protocol chip on the same board?<br/>The tracks are &lt; 5 cm (1.97 in.).</li> </ul>                                                                                                                                                                                                                                                                                      |  |

| HE 30.        | <ul> <li>Are the Latch, Data (IN&amp;OUT), Clock, and /ResReg signals<br/>for the register expansion blocks only used by the INTERBUS<br/>slave protocol chip or by the reset logic that controls it?</li> </ul>                                                                                                                                                                                                                                  |  |

| HE 31.        | <ul> <li>Diagnostic signals</li> <li>The required diagnostic LEDs for this device type (see table) are directly connected to the slave protocol chip and are not controlled via software (with the exception of TR).</li> </ul>                                                                                                                                                                                                                   |  |

| HE 32.        | <ul> <li>The green U<sub>L</sub> LED is directly controlled by the voltage monitor.</li> </ul>                                                                                                                                                                                                                                                                                                                                                    |  |

| HE 33.        | <ul> <li>If the protocol chip diagnostic input I/O Error ("/StatErr" for<br/>IBS SUPI 3) is used, the events that are generated by these<br/>diagnostic messages are simulated and the response is<br/>checked at the INTERBUS master. ****)<br/>The data pattern 0xF0 is output for all OUT data bytes of the<br/>test object. This means it is also possible to test module error<br/>messages by short-circuiting a digital output.</li> </ul> |  |

| <b>HE</b> 34. | - If the protocol chip diagnostic input <i>Reconfiguration Request</i><br>("Conf" for IBS SUPI 3) is used, the events that are generated<br>by this diagnostic message are simulated and the response<br>is checked at the INTERBUS master. ****)            |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>HE</b> 35. | - If the protocol chip diagnostic input <i>MAU Warning</i> ("MAUWS, MAUWR, MAUWH" for IBS SUPI 3) is used, the events that are generated by this diagnostic message are simulated and the response is checked at the INTERBUS master. ****)                  |  |

| <b>HE</b> 36. | - If the protocol chip diagnostic input <i>Microprocessor</i><br><i>Watchdog</i> ("/StatErr" for IBS SUPI 3) is used, the events that<br>are generated by this diagnostic message are simulated and<br>the response is checked at the INTERBUS master. ****) |  |

| <b>HE</b> 37. | - If the protocol chip diagnostic output <i>Alarm</i> ("Alarm" for IBS SUPI 3) is used, the events that are generated by this diagnostic signal at the device are checked. ****)                                                                             |  |

| <b>HE</b> 38. | - If the protocol chip diagnostic output <i>Module Acknowledge</i><br>("/ModAck" for IBS SUPI 3) is used, the events that are<br>generated by this diagnostic signal at the device are<br>checked. ****)                                                     |  |

| <b>HE</b> 39. | <ul> <li>Additional PCP error codes</li> <li>Additional PCP error codes defined by the manufacturer are always assigned error class "8", error code "0" in the additional code.</li> </ul>                                                                   |  |

| No.          | Test Step                                                     | OK *) |

|--------------|---------------------------------------------------------------|-------|

| HE 1         | <ul> <li>All resistors have a tolerance of +/- 1%.</li> </ul> |       |

| LWL          |                                                               |       |

| <b>HE</b> 2. | - All resistors have a tolerance of +/- 10%.                  |       |

| LWL          |                                                               |       |

| <b>HE</b> 3. | - All resistors have a tolerance of +/- 1%.                   |       |

| LWL          |                                                               |       |

| <b>HE</b> 4. | - All resistors have a tolerance of +/- 1%.                   |       |

| LWL          |                                                               |       |

| HE 5.<br>LWL | - Have any other active and passive components (e.g.,<br>Transsorb or suppressor diodes, filters, etc.) been used on/in the<br>INTERBUS data path in addition to those currently used and<br>specified in the circuit versions? |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HE 6.<br>LWL | <ul> <li>Connector pin assignment</li> <li>Has an approved connector type been used? *)</li> <li>Which? (please enter here)</li> </ul>                                                                                          |  |

| HE 7.<br>LWL | - Has an approved type of protocol chip or an approved alternative been used? *)                                                                                                                                                |  |

| HE 8.<br>LWL | - Is optical control enabled? (RF1=RF2=0 for SUPI3 OPC)                                                                                                                                                                         |  |

Manufacturer

Name

Signature